The speed of the analysis of SORD M68 BOOT ROM has slowed down. The reason for the delay is that there are few codes or values left in the disassembler code that can be used as hints. It seems to be impossible for me to guess by looking at the paper and ghidra screen.

So, using the information that is currently available, I decided to have a monitor program recorded on a specific sector of the FDD and directly verify the port with an unknown function from that monitor program.

By analyzing the BOOT ROM, I know that SORD M68 loads only 2kb of sector 1~8 of side 0 of track 1 of FDD#0 to 0x0 address at startup. Therefore, a monitor that works with 2kb is the best choice, but I couldn't find one right away. So I targeted the Universal Monitor(

https://electrelic.com/electrelic/node/1317), which is compact and fully functional, and made a limited-featured version that omits unused functions, and tested if it could run on SORD M68.

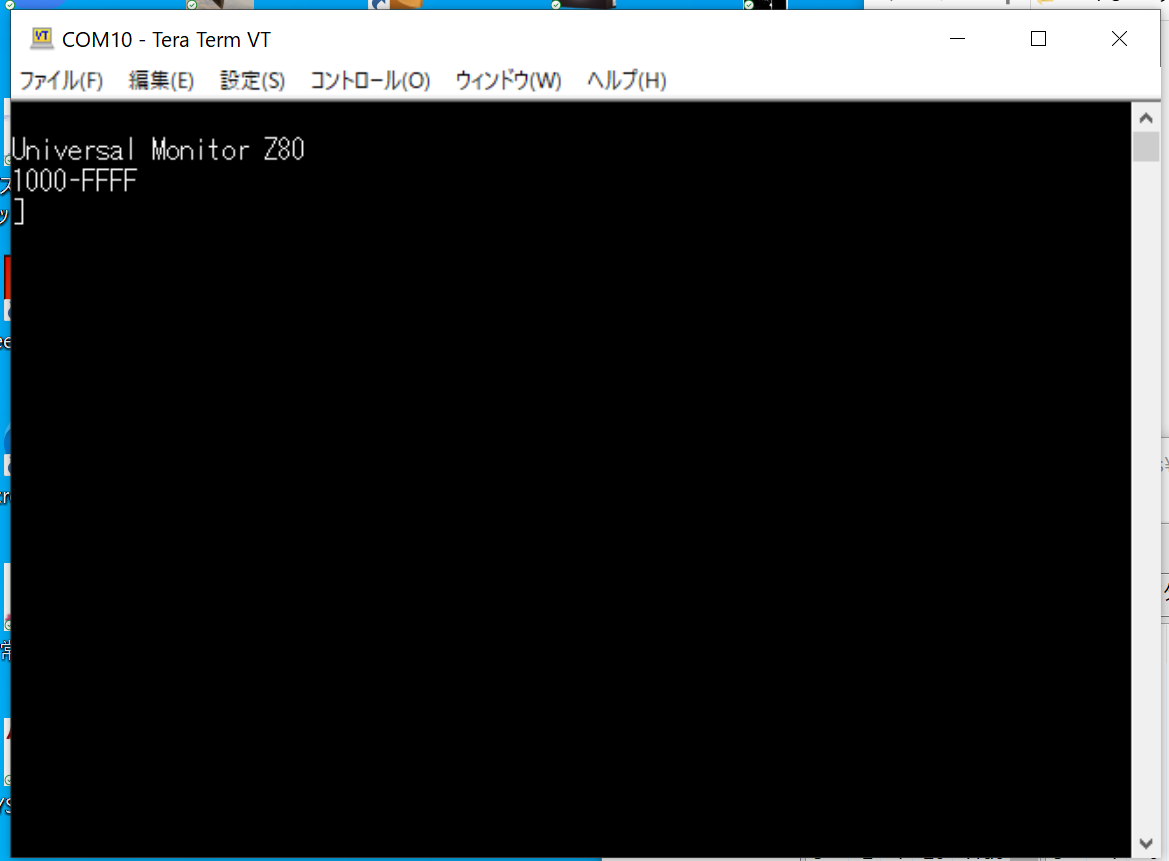

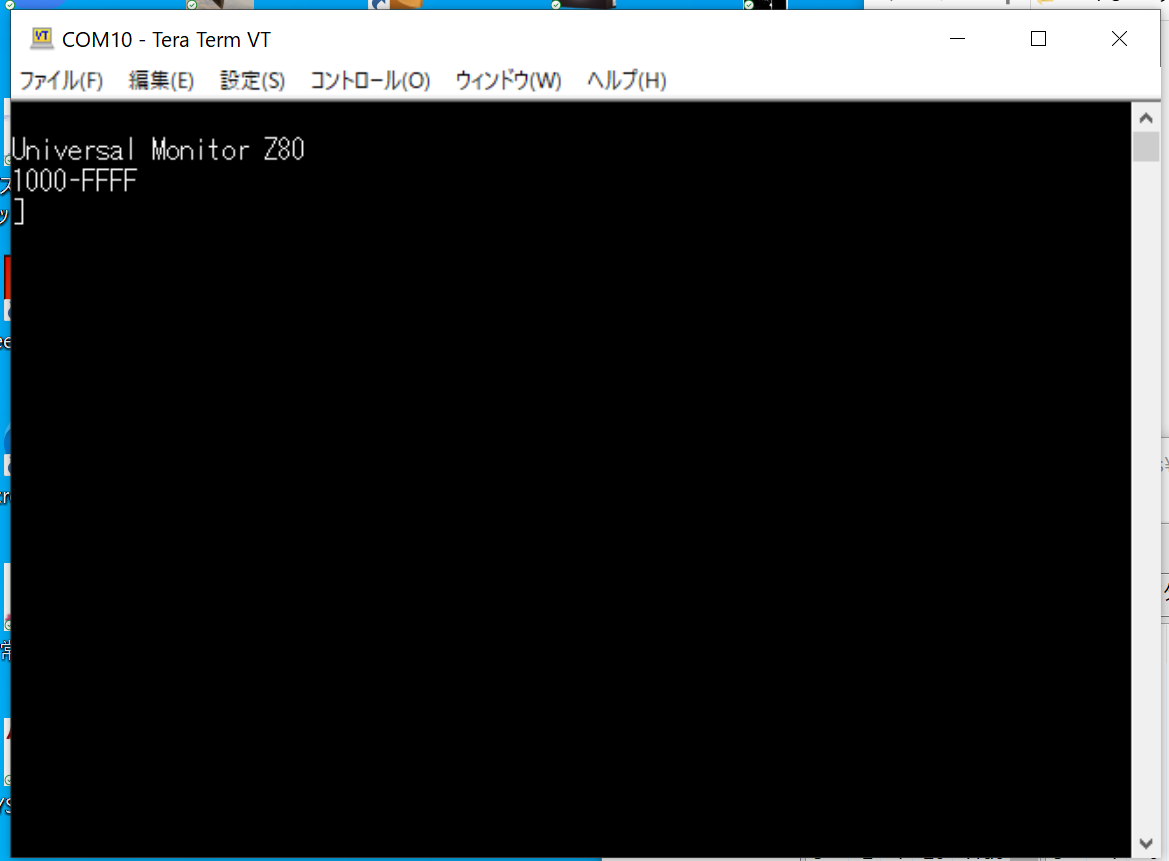

In Serial I/O setup, it is known that Z80CTC is the baud rate generator for Z80SIO, but since Z80CTC is already initialized in BOOT ROM, it does not do anything on Universal Monitor. However, the initial parameters of Z80SIO are different from the current common settings (stop bit 2), so change them to stop bit 1 and no parity. Now I can connect at 9600bps.

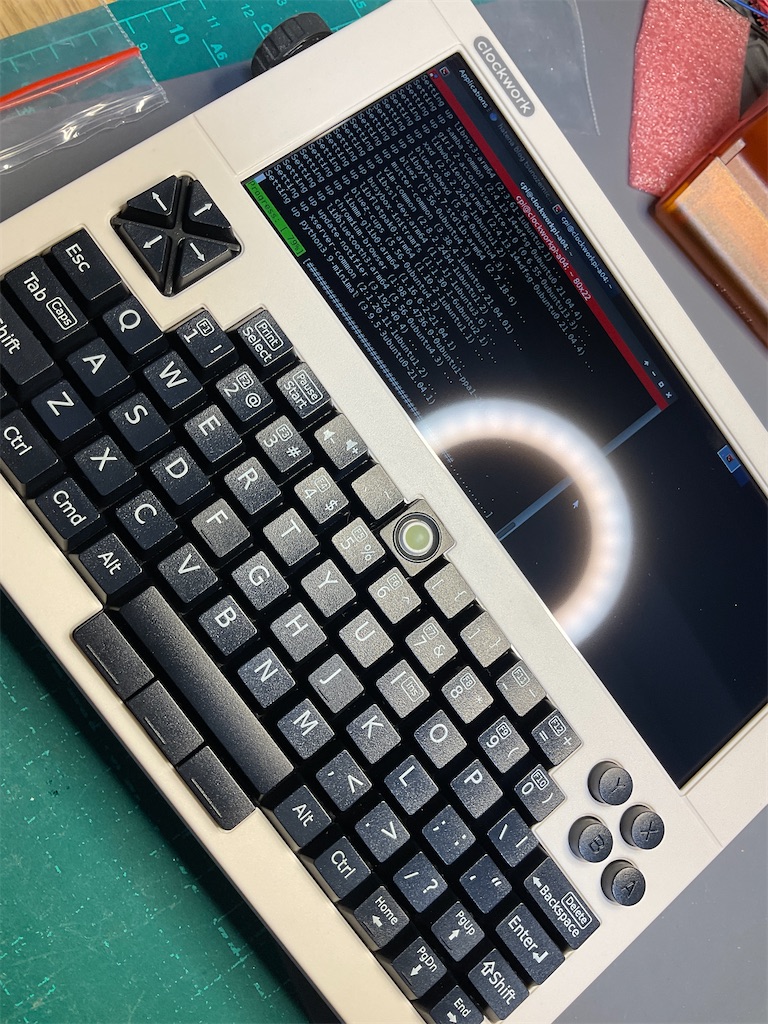

Use L3DiskEx to import the binary file created by assembling the Universal Monitor with limited functionality from track 1, side 0, and sector 1 of the FDD image.

This time, I chose the Dump, Go, Load, and Output commands as the functions to use. At this time, the size of the Universal Monitor was 1647 bytes. Therefore, I wrote 7 sectors to the FDD image. When I inserted the FDD image file that wrote Universal Monitor into the FlashFloppyized GOTEK and booted SORD M68, the following screen came up and Universal Monitor with limited functions started. From now on, I will verify the operation by entering values for unknown ports.